Adding insurance to FPGA applications, functional testing is very important!

Date:2024-02-19 15:41:00 Views:2974

In recent years, with the rise of 5G communication and artificial intelligence, FPGA has been widely applied, and Chuangxin's online testing laboratory often receives samples for testing in this area. After conducting multiple cases, we found that if customers can perform functional testing on the FPGA before starting the machine and confirm whether the status is normal in advance, then the tedious troubleshooting work can be greatly reduced in the later stage. Today we will introduce a case of FPGA functional testing, which can determine whether the device is in a normal state in a few simple steps.

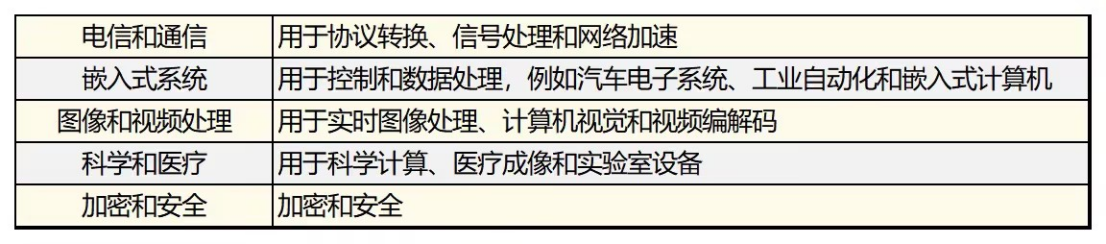

FPGA (Field Programmable Gate Array), also known as Field Programmable Gate Array, is a programmable logic device that has a large number of programmable logic blocks and reconfigurable connection resources. It allows designers to implement custom digital circuits at the hardware level without the need to customize dedicated processors for different applications. This strong flexibility enables FPGA to be widely used in multiple fields, including but not limited to:

FPGA plays a crucial role in the aforementioned fields, and the stability and reliability of its functions are crucial for the overall smooth operation of the system. Therefore, before actually using FPGA, it is necessary for us to conduct a simple functional test to ensure its normal function. If the system cannot run and the FPGA is not tested in the early stage, it will increase the difficulty of troubleshooting work and cause additional time costs.

FPGA can be tested and configured using multiple modes. The following are some common modes used for testing and configuring FPGA:

JTAG mode (Joint Test Action Group mode): JTAG is a standard interface and protocol used for testing and configuring integrated circuits. FPGAs typically have JTAG interfaces, which allow for testing, debugging, and configuration. JTAG also allows for dynamic reconfiguration of FPGAs at runtime.

AS (Active Serial) mode: This is a mode used to configure an FPGA through a serial interface. Usually, configuration data is sent to the FPGA through SPI (Serial Peripheral Interface) or similar serial communication interfaces.

Slave Serial mode: In this mode, the FPGA receives configuration data from external devices through a serial interface. This mode typically involves using external devices (such as microprocessors or FPGAs) as the configuration master.

Passive Serial mode: In this mode, the FPGA receives configuration data through a set of parallel lines (commonly known as TCK, TDI, TMS, and TDO, which are one of the JTAG pins). Unlike Active Serial mode, data is transmitted through parallel interfaces here.

ICAP (Internal Configuration Access Port) mode: ICAP is a mode that allows FPGAs to receive configuration information at runtime. This allows for dynamic partial reconfiguration during FPGA runtime.

PS Configuration Mode: Some FPGAs integrate processor systems, and PS Configuration Mode allows for configuration of the FPGA through a dedicated processor system configuration interface.

The choice of configuration and testing mode usually depends on specific application requirements, as well as development and debugging requirements. Among them, JTAG mode is a universal interface widely used for testing, debugging, and configuration, while other modes are more suitable for specific application scenarios. Our case will be developed using the JTAG model.

In order to better respond to the needs of our customers and ensure efficient testing, Chuangxin Online Testing has independently developed various FPGA detection development boards. We will use the following development board to perform basic functional testing on the FPGA in JTAG configuration mode.

FPGA Test Case Sharing for Chuangxin Online Testing

Based on XC3S2000-4FGG676I (belonging to the Xilinx Spartan-3 series)

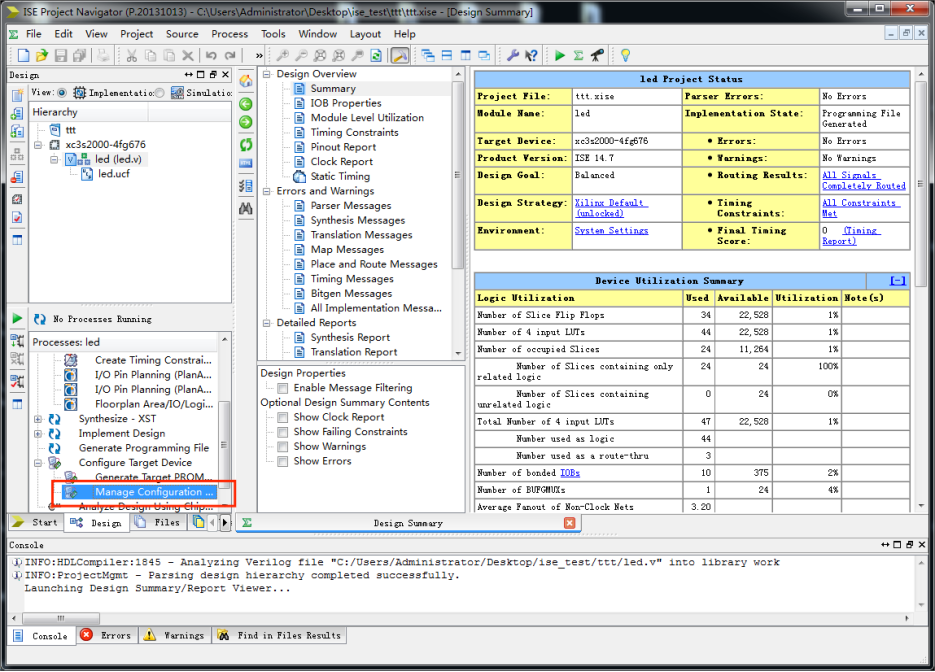

1. Open ISE Design Suite 14.7 software on your computer and click to open "iMPACT". ISE Design Suite is the official development kit of Serenius. With it, we can see the current status of the FPGA and conduct various tests, including import programming and other work.

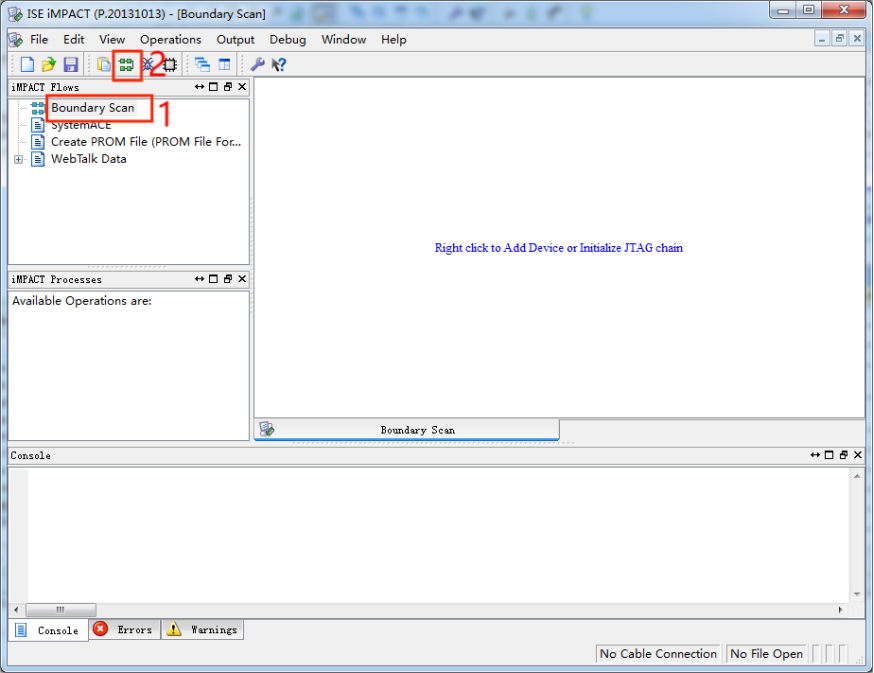

2. Connect the test board, computer, and burner, and click on the recognition device in the ISE Design Suite interface.

3. After successfully identifying the device, we import the test file and click on programming. As shown in the figure, the JTAG circuit is normal and the programming test is successful.

4. Successfully obtained device ID.

5. Successfully obtained device user code.

6. Successfully read device status.

Based on the above steps, it can be concluded that this FPGA can be programmed normally, key information such as device ID and user code can be obtained, and device status can also be read, which proves that this FPGA is functional and usable. In actual computer applications, if there is a problem with the system, it can be ruled out that it is caused by this FPGA.

Functional testing of chips can effectively improve the overall reliability of the system, and professional testing can eliminate failure faults before application. Choosing Chuangxin Online Testing Laboratory, we will provide dedicated service to safeguard your "chip" application.

Weixin Service

Weixin Service

DouYin

DouYin

KuaiShou

KuaiShou